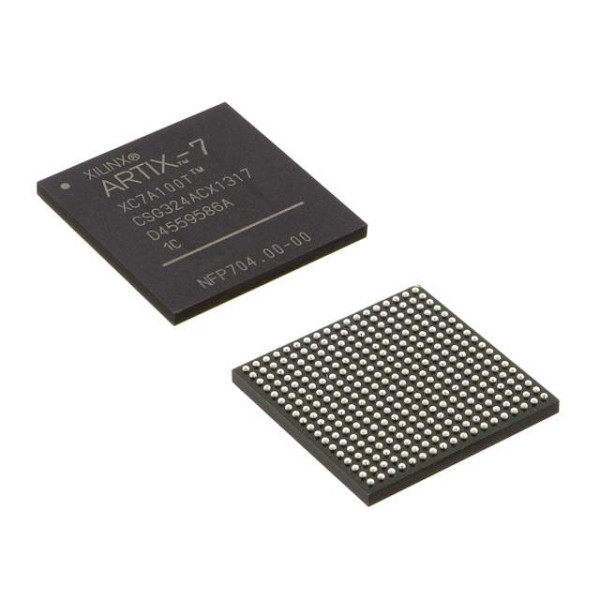

XC7A50T-2CSG324I FPGA – programowalna w terenie tablica bramek XC7A50T-2CSG324I

♠ Opis produktu

| Atrybut produktu | Wartość atrybutu |

| Producent: | Xilinx |

| Kategoria produktu: | FPGA - programowalna w terenie tablica bramek |

| Szereg: | XC7A50T |

| Liczba elementów logicznych: | 52160 LE |

| Liczba wejść/wyjść: | 210 wejść/wyjść |

| Napięcie zasilania - min: | 0,95 V |

| Napięcie zasilania - maks.: | 1,05 V |

| Minimalna temperatura pracy: | -40 stopni Celsjusza |

| Maksymalna temperatura pracy: | + 100 stopni Celsjusza |

| Szybkość transmisji danych: | - |

| Liczba transceiverów: | - |

| Styl montażu: | SMD/SMT |

| Opakowanie / Sprawa: | CSBGA-324 |

| Marka: | Xilinx |

| Rozproszona pamięć RAM: | 600 kbit |

| Wbudowana pamięć blokowa RAM - EBR: | 2700 kbit |

| Wrażliwość na wilgoć: | Tak |

| Liczba bloków macierzy logicznej - LAB: | 4075 LAB |

| Napięcie zasilania roboczego: | 1 napięcie |

| Typ produktu: | FPGA - programowalna w terenie tablica bramek |

| Ilość w opakowaniu fabrycznym: | 1 |

| Podkategoria: | Programowalne układy logiczne |

| Nazwa handlowa: | Artix |

| Waga jednostkowa: | 1 uncja |

♠ Seria FPGA Xilinx® 7 obejmuje cztery rodziny FPGA, które odpowiadają pełnemu zakresowi wymagań systemowych, od niedrogich, niewielkich rozmiarów, wrażliwych na koszty aplikacji o dużej objętości po ultrawysoką przepustowość łączności, pojemność logiczną i możliwości przetwarzania sygnału dla najbardziej wymagających aplikacji o wysokiej wydajności

Seria FPGA Xilinx® 7 obejmuje cztery rodziny FPGA, które odpowiadają na pełen zakres wymagań systemowych, od niedrogich, małych, wrażliwych na koszty, aplikacji o dużej objętości do ultra high-endowej przepustowości łączności, pojemności logicznej i możliwości przetwarzania sygnału dla najbardziej wymagających aplikacji o wysokiej wydajności. Seria FPGA 7 obejmuje:

• Rodzina Spartan®-7: Zoptymalizowana pod kątem niskich kosztów, najniższego poboru mocy i wysokiej wydajności I/O. Dostępna w niedrogiej, bardzo małej obudowie o najmniejszym współczynniku kształtu dla najmniejszej powierzchni PCB.

• Rodzina Artix®-7: Zoptymalizowana do zastosowań o niskim poborze mocy, wymagających szeregowych transceiverów i wysokiej przepustowości DSP i logiki. Zapewnia najniższy całkowity koszt zestawienia materiałów dla aplikacji o dużej przepustowości i wrażliwych na koszty.

• Rodzina Kintex®-7: zoptymalizowana pod kątem najlepszego stosunku ceny do wydajności, z dwukrotnie większą poprawą w porównaniu z poprzednią generacją, umożliwiająca stworzenie nowej klasy układów FPGA.

• Rodzina Virtex®-7: Zoptymalizowana pod kątem najwyższej wydajności i pojemności systemu z 2-krotną poprawą wydajności systemu. Urządzenia o najwyższych możliwościach dzięki technologii połączeń krzemowych (SSI).

Zbudowane na bazie najnowocześniejszej, wysokowydajnej, energooszczędnej (HPL), 28 nm technologii procesowej z bramką metalową o wysokiej stałej dielektrycznej (HKMG), układy FPGA serii 7 umożliwiają niespotykany dotąd wzrost wydajności systemu dzięki przepustowości wejścia/wyjścia wynoszącej 2,9 Tb/s, pojemności 2 milionów komórek logicznych i 5,3 TMAC/s DSP, przy jednoczesnym poborze o 50% mniejszej energii niż urządzenia poprzedniej generacji, oferując w pełni programowalną alternatywę dla układów ASSP i ASIC.

• Zaawansowana, wydajna logika FPGA oparta na technologii rzeczywistych 6-wejściowych tablic odnośników (LUT), konfigurowalna jako pamięć rozproszona.

• 36 KB pamięci blokowej RAM z podwójnym portem i wbudowaną logiką FIFO do buforowania danych na układzie.

• Wysokowydajna technologia SelectIO™ z obsługą interfejsów DDR3 do 1866 Mb/s.

• Szybka łączność szeregowa z wbudowanymi transceiverami wielogigabitowymi o przepustowości od 600 Mb/s do maks. szybkości 6,6 Gb/s do 28,05 Gb/s, oferująca specjalny tryb niskiego poboru mocy, zoptymalizowany pod kątem interfejsów typu chip-to-chip.

• Konfigurowalny przez użytkownika interfejs analogowy (XADC) obejmujący dwa 12-bitowe przetworniki analogowo-cyfrowe 1MSPS z wbudowanymi czujnikami temperatury i zasilania.

• Procesory DSP z mnożnikiem 25 x 18, akumulatorem 48-bitowym i presumatorem zapewniają wydajne filtrowanie, w tym zoptymalizowane symetryczne filtrowanie współczynnikowe.

• Potężne płytki zarządzania zegarem (CMT) łączące bloki pętli synchronizacji fazowej (PLL) i menedżera zegara w trybie mieszanym (MMCM) zapewniają wysoką precyzję i niskie drgania.

• Szybkie wdrażanie przetwarzania wbudowanego dzięki procesorowi MicroBlaze™.

• Zintegrowany blok dla PCI Express® (PCIe) do projektów x8 Gen3 Endpoint i Root Port.

• Szeroka gama opcji konfiguracji, obejmująca obsługę pamięci standardowych, 256-bitowe szyfrowanie AES z uwierzytelnianiem HMAC/SHA-256 oraz wbudowaną funkcję wykrywania i korygowania SEU.

• Niedrogie, łączone drutem, gołe chipy typu flip-chip i obudowy flip-chip o wysokiej integralności sygnału, oferujące łatwą migrację między członkami rodziny w tym samym opakowaniu. Wszystkie opakowania dostępne w wersji bezołowiowej, a wybrane w wersji z opcją Pb.

• Zaprojektowany z myślą o wysokiej wydajności i najniższym zużyciu energii dzięki procesowi 28 nm, HKMG, HPL, technologii przetwarzania napięcia rdzenia 1,0 V i opcji napięcia rdzenia 0,9 V dla jeszcze niższego poboru mocy.