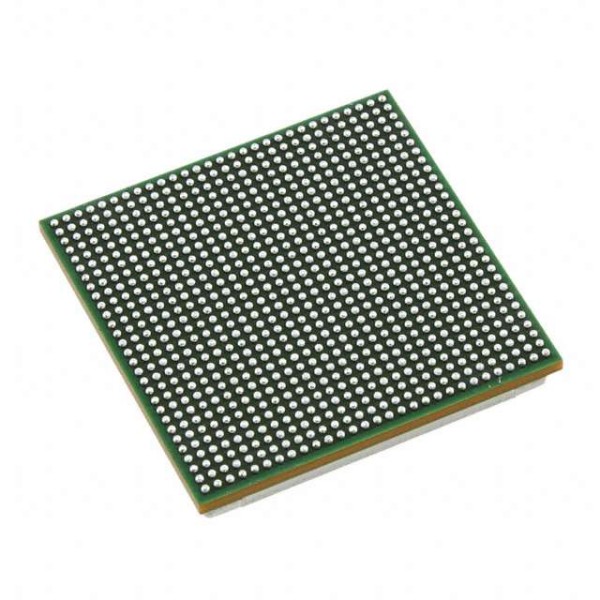

TMS320C6678ACYPA Wielordzeniowy Fix/Float Pt Dig Sig Proc

♠ Opis produktu

| Atrybut produktu | Wartość atrybutu |

| Producent: | Instrumenty Teksasu |

| Kategoria produktu: | Cyfrowe procesory sygnałowe i kontrolery - DSP, DSC |

| Produkt: | Procesory DSP |

| Szereg: | TMS320C6678 |

| Styl montażu: | SMD/SMT |

| Opakowanie / Sprawa: | FCBGA-841 |

| Rdzeń: | C66x |

| Liczba rdzeni: | 8 rdzeni |

| Maksymalna częstotliwość zegara: | Częstotliwość 1 GHz, 1,25 GHz |

| Pamięć instrukcji pamięci podręcznej L1: | 8 x 32 kB |

| Pamięć podręczna danych L1: | 8 x 32 kB |

| Rozmiar pamięci programu: | - |

| Rozmiar pamięci RAM danych: | - |

| Napięcie zasilania roboczego: | 900 mV do 1,1 V |

| Minimalna temperatura pracy: | -40 stopni Celsjusza |

| Maksymalna temperatura pracy: | + 100 stopni Celsjusza |

| Opakowanie: | Taca |

| Marka: | Instrumenty Teksasu |

| Szerokość magistrali danych: | 8 bitów/16 bitów/32 bity |

| Typ instrukcji: | Stały/Zmiennoprzecinkowy |

| MMACS: | 320000 MMACS |

| Wrażliwość na wilgoć: | Tak |

| Liczba wejść/wyjść: | 16 Wejść/Wyjść |

| Liczba timerów/liczników: | 16 Zegar |

| Typ produktu: | DSP - Cyfrowe procesory sygnałowe i kontrolery |

| Ilość w opakowaniu fabrycznym: | 44 |

| Podkategoria: | Procesory i kontrolery wbudowane |

| Napięcie zasilania - maks.: | 1,1 V |

| Napięcie zasilania - min: | 900mV |

| Waga jednostkowa: | 0,252724 uncji |

♠ Wielordzeniowy procesor sygnałowy o stałej i zmiennoprzecinkowej architekturze cyfrowej

Procesor DSP TMS320C6678 to najbardziej wydajny procesor DSP stałoprzecinkowy/zmiennoprzecinkowy oparty na wielordzeniowej architekturze KeyStone firmy TI. Dzięki zastosowaniu nowego i innowacyjnego rdzenia DSP C66x urządzenie to może pracować z szybkością rdzenia do 1,4 GHz. Dla deweloperów szerokiego zakresu aplikacji, takich jak systemy o znaczeniu krytycznym, obrazowanie medyczne, testy i automatyzacja oraz inne aplikacje wymagające wysokiej wydajności, procesor DSP TMS320C6678 firmy TI oferuje łączną częstotliwość DSP 11,2 GHz i umożliwia platformę, która jest energooszczędna i łatwa w użyciu. Ponadto jest w pełni kompatybilny wstecz ze wszystkimi istniejącymi procesorami DSP stałoprzecinkowymi i zmiennoprzecinkowymi rodziny C6000.

Architektura KeyStone firmy TI zapewnia programowalną platformę integrującą różne podsystemy (rdzenie C66x, podsystem pamięci, urządzenia peryferyjne i akceleratory) i wykorzystuje kilka innowacyjnych komponentów i technik w celu maksymalizacji komunikacji wewnątrzurządzeniowej i międzyurządzeniowej, co pozwala różnym zasobom DSP działać wydajnie i bezproblemowo. Centralnym elementem tej architektury są kluczowe komponenty, takie jak Multicore Navigator, który umożliwia wydajne zarządzanie danymi między różnymi komponentami urządzenia. TeraNet to nieblokująca struktura przełącznika umożliwiająca szybki i bezkonfliktowy wewnętrzny ruch danych. Wielordzeniowy kontroler pamięci współdzielonej umożliwia bezpośredni dostęp do pamięci współdzielonej i zewnętrznej bez korzystania z pojemności struktury przełącznika.

• Osiem rdzeniowych podsystemów DSP TMS320C66x™ (C66x CorePacs), każdy z

– 1,0 GHz, 1,25 GHz lub 1,4 GHz C66x Rdzeń procesora stałego/zmiennoprzecinkowego

› 44,8 GMAC/rdzeń dla punktu stałego @ 1,4 GHz

› 22,4 GFLOP/rdzeń dla operacji zmiennoprzecinkowych przy 1,4 GHz

– Pamięć

› 32K bajtów L1P na rdzeń

› 32K bajtów L1D na rdzeń

› 512K bajtów lokalnych L2 na rdzeń

• Kontroler pamięci współdzielonej wielordzeniowej (MSMC)

– 4096 KB pamięci MSM SRAM współdzielonej przez osiem procesorów DSP C66x CorePacs

– Jednostka ochrony pamięci dla pamięci MSM SRAM i DDR3_EMIF

• Nawigator wielordzeniowy

– 8192 Wielofunkcyjne kolejki sprzętowe z menedżerem kolejek

– DMA oparte na pakietach dla transferów bez narzutu

• Koprocesor sieciowy

– Akcelerator pakietów umożliwia obsługę

› Transport Samolotowy IPsec, GTP-U, SCTP, PDCP

› L2 User Plane PDCP (RoHC, szyfrowanie powietrzne)

› Przepustowość 1 Gb/s z prędkością 1,5 MPaktów na sekundę

– Silnik akceleratora zabezpieczeń umożliwia obsługę

› IPSec, SRTP, 3GPP, interfejs WiMAX Air i zabezpieczenia SSL/TLS

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (256-bitowy skrót), MD5

› Prędkość szyfrowania do 2,8 Gb/s

• Urządzenia peryferyjne

– Cztery pasy SRIO 2.1

› Obsługa operacji GBaud 1,24/2,5/3,125/5 na pas

› Obsługuje bezpośrednie wejście/wyjście, przekazywanie komunikatów

› Obsługuje cztery konfiguracje łącza 1×, dwie 2×, jedną 4× i dwie 1× + jedną 2×

– PCIe Gen2

› Pojedynczy port obsługujący 1 lub 2 pasy

› Obsługuje do 5 GBaud na pasmo

– Hiperłącze

› Obsługuje połączenia z innymi urządzeniami architektury KeyStone, zapewniając skalowalność zasobów

› Obsługuje do 50 Gbaud

– Podsystem przełącznika Gigabit Ethernet (GbE)

› Dwa porty SGMII

› Obsługuje pracę z szybkością 10/100/1000 Mb/s

– 64-bitowy interfejs DDR3 (DDR3-1600)

› 8G bajtowa adresowalna przestrzeń pamięci

– 16-bitowy EMIF

– Dwa porty szeregowe telekomunikacyjne (TSIP)

› Obsługuje 1024 DS0 na TSIP

› Obsługuje 2/4/8 pasm przy 32,768/16,384/8,192 Mb/s na pasmo

– Interfejs UART

– I2

Interfejs C

– 16 pinów GPIO

– Interfejs SPI

– Moduł semafora

– Szesnaście 64-bitowych timerów

– Trzy układy PLL na chipie

• Temperatura komercyjna:

– 0°C do 85°C

• Rozszerzona temperatura:

– od -40°C do 100°C

• Systemy o znaczeniu krytycznym

• Systemy komputerowe o wysokiej wydajności

• Komunikacja

• Dźwięk

• Infrastruktura wideo

• Obrazowanie

• Analityka

• Sieciowanie

• Przetwarzanie multimediów

• Automatyka przemysłowa

• Automatyzacja i kontrola procesów