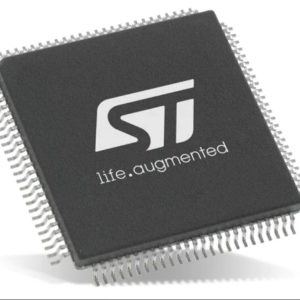

SPC563M64L5COAR 32-bitowe mikrokontrolery – MCU 32-BIT Wbudowany MCU 80 MHz, 1,5 MB

♠ Opis produktu

| Atrybut produktu | Wartość atrybutu |

| Producent: | STMicroelektronika |

| Kategoria produktu: | Mikrokontrolery 32-bitowe - MCU |

| RoHS: | Bliższe dane |

| Szereg: | SPC563M64L5 |

| Styl montażu: | SMD/SMT |

| Opakowanie/Sprawa: | LQFP-144 |

| Rdzeń: | e200z335 |

| Rozmiar pamięci programu: | 1,5 MB |

| Rozmiar pamięci RAM danych: | 94 kB |

| Szerokość magistrali danych: | 32 bit |

| Rozdzielczość ADC: | 2 x 8 bitów/10 bitów/12 bitów |

| Maksymalna częstotliwość zegara: | 80MHz |

| Liczba wejść/wyjść: | 105 Wejść/Wyjść |

| Napięcie zasilania - min: | 5 V |

| Napięcie zasilania - maks.: | 5 V |

| Minimalna temperatura pracy: | -40 stopni Celsjusza |

| Maksymalna temperatura pracy: | + 125 stopni Celsjusza |

| Kwalifikacja: | AEC-Q100 |

| Opakowanie: | Rolka |

| Opakowanie: | Przetnij taśmę |

| Opakowanie: | Kołowrotek z myszką |

| Marka: | STMicroelektronika |

| Wrażliwość na wilgoć: | Tak |

| Typ produktu: | Mikrokontrolery 32-bitowe - MCU |

| Ilość w opakowaniu fabrycznym: | 500 |

| Podkategoria: | Mikrokontrolery - MCU |

| Waga jednostkowa: | 1,290 grama |

♠ 32-bitowy układ MCU oparty na architekturze Power Architecture® do zastosowań w układach napędowych samochodów

Te 32-bitowe mikrokontrolery samochodowe to rodzina urządzeń System-on-Chip (SoC), które zawierają wiele nowych funkcji połączonych z technologią CMOS 90 nm o wysokiej wydajności, aby zapewnić znaczną redukcję kosztów na funkcję i znaczną poprawę wydajności. Zaawansowany i ekonomiczny rdzeń procesora hosta tej rodziny kontrolerów samochodowych jest zbudowany w technologii Power Architecture®. Ta rodzina zawiera ulepszenia, które poprawiają dopasowanie architektury do aplikacji wbudowanych, obejmuje dodatkowe wsparcie instrukcji dla przetwarzania sygnału cyfrowego (DSP), integruje technologie — takie jak ulepszona jednostka procesora czasu, ulepszony przetwornik analogowo-cyfrowy w kolejce, sieć Controller Area Network i ulepszony modułowy system wejścia-wyjścia — które są ważne dla dzisiejszych aplikacji układów napędowych niższej klasy. Urządzenie ma jeden poziom hierarchii pamięci składający się z maksymalnie 94 KB pamięci SRAM na układzie i maksymalnie 1,5 MB wewnętrznej pamięci flash. Urządzenie ma również interfejs zewnętrznej magistrali (EBI) do „kalibracji”.

■ Pojedynczy problem, 32-bitowy kompleks rdzeni procesora e200z335 zgodny z architekturą Power Architecture® Book E

– Zawiera ulepszenia kodowania o zmiennej długości (VLE) w celu zmniejszenia rozmiaru kodu

■ 32-kanałowy kontroler bezpośredniego dostępu do pamięci (DMA)

■ Kontroler przerwań (INTC) obsługujący 364 źródła przerwań o wybieralnym priorytecie: 191 źródeł przerwań peryferyjnych, 8 przerwań programowych i 165 przerwań zarezerwowanych.

■ Pętla synchronizacji fazowej z modulacją częstotliwości (FMPLL)

■ Kalibracja zewnętrznego interfejsu magistrali (EBI)(a)

■ Jednostka Integracji Systemów (SIU)

■ Do 1,5 MB wbudowanej pamięci Flash z kontrolerem Flash

– Akcelerator pobierania dla pojedynczego cyklu dostępu do pamięci Flash @80 MHz

■ Do 94 KB pamięci RAM na układzie scalonym (w tym do 32 KB pamięci RAM w trybie gotowości)

■ Moduł wspomagający rozruch (BAM)

■ 32-kanałowa ulepszona jednostka procesora czasu (eTPU) drugiej generacji

– 32 standardowe kanały eTPU

– Udoskonalenia architektoniczne mające na celu zwiększenie efektywności kodu i zwiększenie elastyczności

■ 16-kanałowy ulepszony modułowy system wejścia-wyjścia (eMIOS)

■ Ulepszony przetwornik analogowo-cyfrowy z kolejką (eQADC)

■ Filtr dziesiątkujący (część eQADC)

■ Czujnik temperatury matrycy krzemowej

■ 2 moduły Deserial Serial Peripheral Interface (DSPI) (zgodne z magistralą Microsecond)

■ 2 ulepszone moduły interfejsu komunikacji szeregowej (eSCI) zgodne z LIN

■ 2 moduły Controller Area Network (FlexCAN) obsługujące CAN 2.0B

■ Kontroler portu Nexus (NPC) zgodny z normą IEEE-ISTO 5001-2003

■ Obsługa IEEE 1149.1 (JTAG)

■ Interfejs Nexus

■ Wbudowany regulator napięcia, który zapewnia wewnętrzne zasilanie 1,2 V i 3,3 V z zewnętrznego źródła 5 V.

■ Zaprojektowany dla LQFP144 i LQFP176