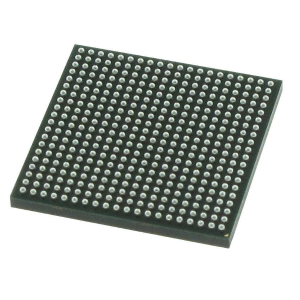

LCMXO1200C-3TN144I FPGA – programowalna tablica bramek 1200 LUT 113 IO 1,8 /2,5/3,3 V -3 Spd I

♠ Opis produktu

| Atrybut produktu | Wartość atrybutu |

| Producent: | Krata |

| Kategoria produktu: | FPGA - programowalna w terenie tablica bramek |

| RoHS: | Bliższe dane |

| Szereg: | LCMXO1200C |

| Liczba elementów logicznych: | 1200 LE |

| Liczba wejść/wyjść: | 113 Wejść/Wyjść |

| Napięcie zasilania - min: | 1,71 V |

| Napięcie zasilania - maks.: | 3,465 V |

| Minimalna temperatura pracy: | -40 stopni Celsjusza |

| Maksymalna temperatura pracy: | + 100 stopni Celsjusza |

| Szybkość transmisji danych: | - |

| Liczba transceiverów: | - |

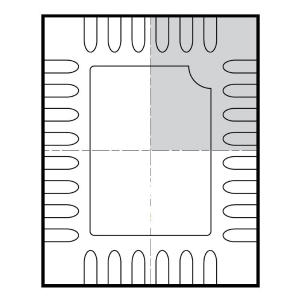

| Styl montażu: | SMD/SMT |

| Opakowanie/Sprawa: | TQFP-144 |

| Opakowanie: | Taca |

| Marka: | Krata |

| Rozproszona pamięć RAM: | 6,4 kbitów |

| Wbudowana pamięć blokowa RAM - EBR: | 9,2 kbitów |

| Wysokość: | 1,4 mm |

| Długość: | 20 mm |

| Maksymalna częstotliwość robocza: | 500MHz |

| Wrażliwość na wilgoć: | Tak |

| Liczba bloków macierzy logicznej - LAB: | 150 LAB |

| Prąd zasilania roboczego: | 21 miliamperów |

| Napięcie zasilania roboczego: | 1,8 V/2,5 V/3,3 V |

| Typ produktu: | FPGA - programowalna w terenie tablica bramek |

| Ilość w opakowaniu fabrycznym: | 60 |

| Podkategoria: | Programowalne układy logiczne |

| Całkowita pamięć: | 15,6 kbitów |

| Szerokość: | 20 mm |

| Waga jednostkowa: | 1,319 grama |

Nieulotny, nieskończenie rekonfigurowalny

• Natychmiastowe włączanie – uruchamia się w mikrosekundy

• Pojedynczy układ, nie wymaga zewnętrznej pamięci konfiguracyjnej

• Doskonałe bezpieczeństwo konstrukcji, brak strumienia bitów do przechwycenia

• Rekonfiguracja logiki opartej na pamięci SRAM w milisekundach

• Pamięć SRAM i pamięć nieulotna programowalna poprzez port JTAG

• Obsługuje programowanie w tle pamięci nieulotnej

Tryb uśpienia

• Pozwala na 100-krotną redukcję prądu statycznego

Rekonfiguracja TransFR™ (TFR)

• Aktualizacja logiki w terenie podczas pracy systemu

Wysoka gęstość wejścia/wyjścia do logiki

• 256 do 2280 LUT4

• 73 do 271 wejść/wyjść z rozbudowanymi opcjami pakietów

• Obsługiwana migracja gęstości

• Opakowanie bez ołowiu/zgodne z dyrektywą RoHS

Pamięć wbudowana i rozproszona

• Do 27,6 kbitów pamięci RAM sysMEM™ Embedded Block

• Do 7,7 kbitów rozproszonej pamięci RAM

• Dedykowana logika sterowania FIFO

Elastyczny bufor wejścia/wyjścia

• Programowalny bufor sysIO™ obsługuje szeroką gamę interfejsów:

Wersja: 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, magistrala LVDS, LVPECL, RSDS

sysCLOCK™ PLL

• Do dwóch analogowych PLL na urządzenie

• Mnożenie, dzielenie i przesuwanie fazy zegara

Wsparcie na poziomie systemu

• Norma IEEE 1149.1 Skanowanie granic

• Oscylator pokładowy

• Urządzenia działają z zasilaniem 3,3 V, 2,5 V, 1,8 V lub 1,2 V

• Programowanie w systemie zgodne ze standardem IEEE 1532